02166766957 -02166766927

info@atrinelec.com

@atrinelec

# FSK power line transceiver

#### **General features**

- Half-duplex frequency shift keying (FSK) transceiver

- Integrated power line driver with programmable voltage and current control

- Programmable mains access:

- Synchronous

- Asynchronous

- Single supply voltage (from 7.5V up to 13.5V)

- Very low power consumption (I<sub>q</sub> = 5mA)

- Integrates 5V voltage regulator (up to 50mA) with short circuit protection

- Integrated 3.3V voltage regulator (up to 50mA) with short circuit protection

- 3.3V or 5V digital supply

- 8 Programmable transmission frequencies

- Programmable baud rate up to 4800BPS

- Receiving sensitivity up to 250µV<sub>RMS</sub>

- Suitable for applications in accordance with EN 50065 Cenelec specification

- Carrier or preamble detection

- Band in use detection

- Programmable control register

- Watchdog timer

- 8 or 16 Bit header recognition

- ST7537 and ST7538 compatible

- UART/SPI host interface

## **Description**

The ST7540 is a Half Duplex synchronous/asynchronous FSK Modem designed for power line communication network applications. It operates from a single supply voltage and integrates a line driver and two linear regulators for 5V and 3.3V. The device operation is controlled by means of an internal register, programmable through the synchronous serial interface. Additional functions as watchdog, clock output, output voltage and current control, preamble detection, time-out and band in use are included. Realized in Multipower BCD5 technology that allows to integrate DMOS, Bipolar and CMOS structures in the same chip.

#### **Order codes**

| Part number | Package                | Packaging     |

|-------------|------------------------|---------------|

| ST7540      | HTSSOP28 (Exposed Pad) | Tube          |

| ST7540TR    | HTSSOP28 (Exposed Pad) | Tape and reel |

Contents ST7540

# **Contents**

| 1 | Bloc | k diagram                                   |

|---|------|---------------------------------------------|

| 2 | Pin  | settings 5                                  |

|   | 2.1  | Pin connection                              |

|   | 2.2  | Pin description                             |

| 3 | Elec | trical data7                                |

|   | 3.1  | Maximum ratings 7                           |

|   | 3.2  | Thermal data                                |

|   | 3.3  | Recommended operating conditions 8          |

| 4 | Elec | trical characteristics9                     |

| 5 | Crys | stal resonator and external clock15         |

| 6 | Fund | ctional description16                       |

|   | 6.1  | Carrier frequencies                         |

|   | 6.2  | Baud rates 16                               |

|   | 6.3  | Mark and space frequencies                  |

|   | 6.4  | ST7540 Mains access                         |

|   | 6.5  | Host processor interface                    |

|   |      | 6.5.1 Communication between Host and ST7540 |

|   |      | 6.5.2 Control register access               |

|   | 6.6  | Receiving mode                              |

|   | 6.7  | Transmission mode                           |

|   | 6.8  | Control register                            |

ST7540 Contents

| 7 | Auxi | liary analog and digital functions | 36 |

|---|------|------------------------------------|----|

|   | 7.1  | Band in use                        | 36 |

|   | 7.2  | Time out                           | 36 |

|   | 7.3  | Reset & watchdog                   | 37 |

|   | 7.4  | Output clock                       | 37 |

|   | 7.5  | Output voltage level freeze        | 37 |

|   | 7.6  | Extended control register          | 37 |

|   | 7.7  | Under voltage lock out             | 38 |

|   | 7.8  | Thermal shutdown                   | 38 |

|   | 7.9  | 5V Voltage regulator               | 38 |

|   | 7.10 | 3.3V Voltage regulator             | 38 |

|   | 7.11 | Power-up procedure                 | 38 |

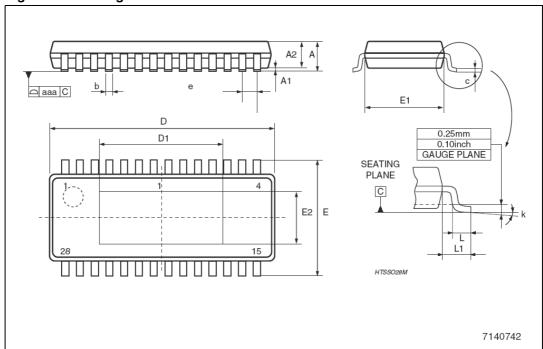

| 8 | Mech | nanical data                       | 41 |

| 9 | Revi | sion history                       | 43 |

Block diagram ST7540

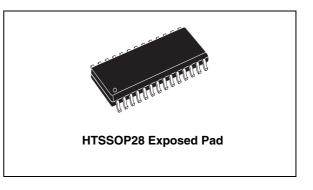

# 1 Block diagram

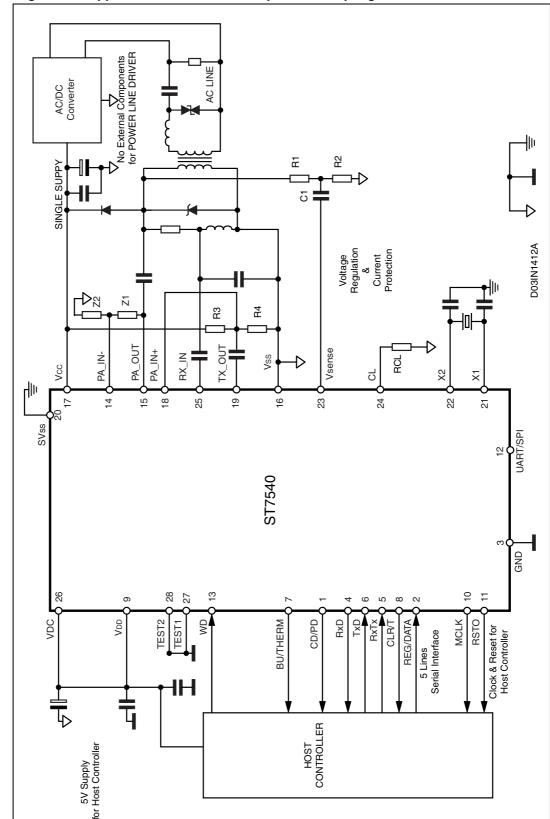

Figure 1. Block diagram

ST7540 Pin settings

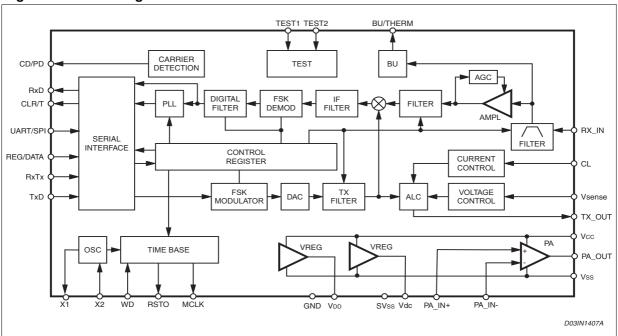

# 2 Pin settings

### 2.1 Pin connection

Figure 2. Pin connection (top view)

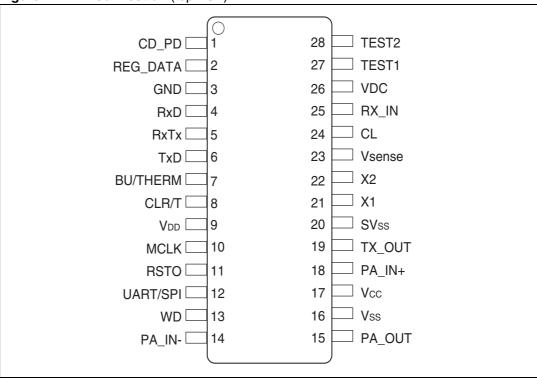

# 2.2 Pin description

Table 1. Pin description

| N° | Name     | Туре                                     | Description                                                                                                                                         |

|----|----------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | CD_PD    | Digital/Output                           | Carrier, preamble or frame header detect output.  "1" No carrier, preamble or frame header detected  "0" Carrier, preamble or frame header detected |

| 2  | REG_DATA | Digital/Input<br>with internal pull-down | Mains or control register access selector "1" - Control register access "0" - Mains access                                                          |

| 3  | GND      | Supply                                   | Digital ground                                                                                                                                      |

| 4  | RxD      | Digital/Output                           | RX data output.                                                                                                                                     |

| 5  | RxTx     | Digital/Input<br>with internal pull-up   | Rx or Tx mode selection input. "1" - RX Session "0" - TX Session                                                                                    |

| 6  | TxD      | Digital/Input<br>with internal pull-down | TX data input.                                                                                                                                      |

**577**

Pin settings ST7540

Table 1. Pin description (continued)

| N° | Name                   | Type                                     | Description                                                                                                                                                                                                                                                     |

|----|------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7  | BU/THERM               | Digital/Output                           | Band in use/Thermal Shutdown event detection output. In Rx mode: "1" Signal within the programmed band "0" No signal within the programmed band In Tx mode: "1" - Thermal Shutdown event occurred "0" - No Thermal Shutdown event occurred (signal not latched) |

| 8  | CLR/T                  | Digital/Output                           | Synchronous mains access clock or control register access clock                                                                                                                                                                                                 |

| 9  | $V_{DD}$               | Supply/Power                             | Digital supply voltage or 3.3V voltage regulator output                                                                                                                                                                                                         |

| 10 | MCLK                   | Digital/Output                           | Master clock output                                                                                                                                                                                                                                             |

| 11 | RSTO                   | Digital/Output                           | Power ON or watchdog reset output                                                                                                                                                                                                                               |

| 12 | UART/SPI               | Digital/Input<br>with internal pull-down | Interface type: "0" - Serial peripheral interface "1" - UART interface                                                                                                                                                                                          |

| 13 | WD                     | Digital/Input with internal pull-up      | Watchdog input. The internal watchdog counter is cleared on the falling edges.                                                                                                                                                                                  |

| 14 | PA_IN-                 | Analog/Input                             | Power line amplifier inverting input                                                                                                                                                                                                                            |

| 15 | PA_OUT                 | Power/Output                             | Power line amplifier output                                                                                                                                                                                                                                     |

| 16 | V <sub>SS</sub>        | Supply                                   | Power analog ground                                                                                                                                                                                                                                             |

| 17 | V <sub>CC</sub>        | Supply                                   | Power supply voltage                                                                                                                                                                                                                                            |

| 18 | PA_IN+                 | Analog/Input                             | Power line amplifier not inverting input                                                                                                                                                                                                                        |

| 19 | TX_OUT                 | Analog/Output                            | Small signal analog transmit output                                                                                                                                                                                                                             |

| 20 | SV <sub>SS</sub>       | Supply                                   | Analog signal ground                                                                                                                                                                                                                                            |

| 21 | X1                     | Analog/Output                            | Crystal oscillator output                                                                                                                                                                                                                                       |

| 22 | X2                     | Analog/Input                             | Crystal oscillator input - or external clock input                                                                                                                                                                                                              |

| 23 | V <sub>SENSE</sub> (1) | Analog/Input                             | Output voltage sensing input for the voltage control loop                                                                                                                                                                                                       |

| 24 | CL <sup>(2)</sup>      | Analog/Input                             | Current limiting feedback. A resistor between CL and SV <sub>SS</sub> sets the PLI current limiting value. An integrated 80pF filtering input capacitance is present on this pin.                                                                               |

| 25 | RX_IN                  | Analog/Input                             | Receiving analog input                                                                                                                                                                                                                                          |

| 26 | VDC                    | Power                                    | 5V voltage regulator output                                                                                                                                                                                                                                     |

| 27 | TEST1                  | Digital/Input<br>with internal pull-down | Test input. Must be connected to GND.                                                                                                                                                                                                                           |

| 28 | TEST2                  | Analog/Input                             | Test input. Must be connected SV <sub>SS</sub>                                                                                                                                                                                                                  |

<sup>1.</sup> Cannot be left floating

<sup>2.</sup> Cannot be left floating

ST7540 Electrical data

## 3 Electrical data

## 3.1 Maximum ratings

Table 2. Absolute maximum ratings

| Symbol                                           | Parameter                                                                   | Value                             | Unit  |

|--------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------|-------|

| V <sub>CC</sub>                                  | Power supply voltage                                                        | -0.3 to + 14                      | V     |

| V <sub>DD</sub>                                  | Digital supply voltage                                                      | -0.3 to +5.5                      | V     |

| SV <sub>SS</sub> /GND                            | Voltage between SV <sub>SS</sub> and GND                                    | -0.3 to +0.3                      | V     |

| V <sub>I</sub>                                   | Digital input voltage                                                       | GND - 0.3 to V <sub>DD</sub> +0.3 | V     |

| V <sub>O</sub>                                   | Digital output voltage                                                      | GND - 0.3 to V <sub>DD</sub> +0.3 | V     |

| Io                                               | Digital output current                                                      | -2 to +2                          | mA    |

| V <sub>sense</sub> ,<br>X2,PA_IN-<br>,PA_IN+, CL | Voltage range at Vsense, X2, PA_IN-, PA_IN+, CL Inputs                      | SV <sub>SS</sub> - 0.3 to 5.6     | V     |

| RX_IN                                            | Voltage range at RX_IN input                                                | -5.6 to 5.6                       | V     |

| TX_OUT, X1                                       | Voltage range at TX_OUT, X1 outputs                                         | SV <sub>SS</sub> - 0.3 to 5.6     | ٧     |

| PA_OUT                                           | Voltage range at powered PA_OUT Output                                      | $V_{SS}$ - 0.3 to + $V_{CC}$ +0.3 | V     |

| I(PA_OUT)                                        | Power line driver output current (1)                                        | 650                               | mArms |

| T <sub>A</sub>                                   | Operating ambient temperature                                               | -40 to +85                        | °C    |

| T <sub>STG</sub>                                 | Storage temperature                                                         | -50 to 150                        | °C    |

| RxD,<br>PA_OUT Pin                               | Maximum withstanding voltage range Test condition: CDF-AEC-Q100-002- "Human | ±1750                             | V     |

| Other pins                                       | Body Model" Acceptance criteria: "Normal Performance"                       | ±2000                             | V     |

<sup>1.</sup> This current is intended as not repetitive pulse current

## 3.2 Thermal data

Table 3. Thermal data

| Symbol             | Parameter                                                               | HTSSOP28<br>Exposed Pad | Unit |

|--------------------|-------------------------------------------------------------------------|-------------------------|------|

| R <sub>thJA1</sub> | Maximum thermal resistance junction-ambient steady state <sup>(1)</sup> | 35                      | °C/W |

| R <sub>thJA2</sub> | Maximum thermal resistance junction-ambient Steady State <sup>(2)</sup> | 70                      | °C/W |

<sup>1.</sup> Mounted on Multilayer PCB with a dissipating surface on the bottom side of the PCB

<sup>2.</sup> It is the same condition of the point above, without any heatsinking surface on the board.

Electrical data ST7540

# 3.3 Recommended operating conditions

Table 4. Recommended operating conditions

| Symbol                            | Parameter                                                                           | Test Condition                                                           | Value                | Unit            |

|-----------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------|-----------------|

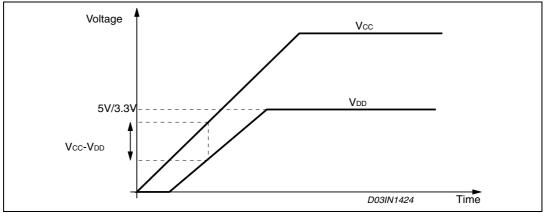

| V <sub>CC</sub>                   | Max allowed slope during Power-up                                                   |                                                                          | 100                  | V/ms            |

| I(V <sub>CC</sub> )               | Powered analog supply<br>Current with digital supply<br>provided externally         | Maximum total current                                                    | 650                  | mArms           |

| V <sub>CC</sub> - V <sub>DD</sub> | Maximum voltage Difference between V <sub>CC</sub> and VDD during power-up sequence | V <sub>DD</sub> < 4.75V with 5V<br>Digital supply provided<br>externally | 1.2                  | V               |

| V <sub>PA_OUT</sub>               | Output voltage swing for PA_OUT pin                                                 |                                                                          | V <sub>CC</sub> -4.5 | V <sub>PP</sub> |

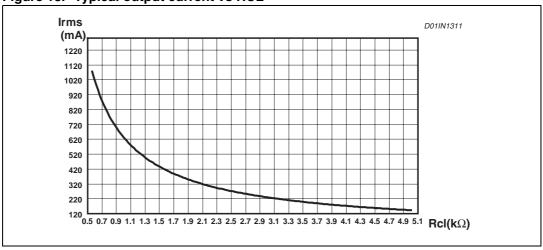

| I(PA_OUT)                         | Maximum output transmitting current in programmable current limiting                | $R_{cl}$ = 1.4kΩ; $R_{LOAD}$ =1Ω (as in <i>Figure 17</i> )               | 500                  | mArms           |

# 4 Electrical characteristics

**Table 5. Electrical characteristics**

(  $V_{DD}$  = +5V,  $V_{CC}$  =+9 V,  $V_{SS}$  =  $SV_{SS}$  = GND = 0V,-40°C  $\leq$   $T_A$   $\leq$  85°C,  $T_J$  < 125°C, unless otherwise specified)

| Symbol              | Parameter                                              | Test condition                                      | Min.                   | Тур. | Max.         | Unit  |

|---------------------|--------------------------------------------------------|-----------------------------------------------------|------------------------|------|--------------|-------|

| V <sub>DD</sub>     | Digital supply voltages                                | 5V Digital supply provided externally               | 4.75                   | 5    | 5.25         | V     |

| V <sub>CC</sub>     | Power supply voltage                                   |                                                     | 7.5                    |      | 13.5         | ٧     |

| I(V <sub>DD</sub> ) | Digital input supply                                   | Transmission & receiving mode (MCLK = 4MHz),no load |                        |      | 3.5          | mA    |

| I(VDD)              | current                                                | Transmission & Receiving mode (MCLK = OFF), no load |                        |      | 1.5          | mA    |

|                     | Power supply current                                   | TX mode, no load                                    |                        |      | 60           | mArms |

| I(V <sub>CC</sub> ) | current with digital supply provided externally        | RX mode                                             |                        |      | 5            | mArms |

| UVLO                | Under voltage lock out<br>Threshold on V <sub>CC</sub> |                                                     | 3.7                    | 3.9  | 4.1          | V     |

| UVLO <sub>HYS</sub> | UVLO Hysteresis on V <sub>CC</sub>                     |                                                     |                        | 340  |              | mV    |

| Digital I/O         |                                                        |                                                     |                        |      |              |       |

| R <sub>down</sub>   | Internal pull down resistor                            |                                                     | -30%                   | 100  | +30%         | kΩ    |

| R <sub>up</sub>     | Internal pull up resistor                              |                                                     | -30%                   | 100  | +30%         | kΩ    |

| Digital I/O - 5\    | / digital supply                                       |                                                     |                        |      | •            |       |

| V <sub>IH</sub>     | High logic level input voltage                         |                                                     | 2                      |      |              | V     |

| V <sub>IL</sub>     | Low logic level input voltage                          |                                                     |                        |      | 1.2          | V     |

| V <sub>OH</sub>     | High logic level output voltage                        | I <sub>OH</sub> = -2mA                              | V <sub>DD</sub> - 0.45 |      |              | V     |

| V <sub>OL</sub>     | Low logic level output voltage                         | I <sub>OL</sub> = 2mA                               |                        |      | GND<br>+ 0.3 | V     |

| Digital I/O - 3.    | 3V digital supply                                      |                                                     |                        |      |              |       |

| V <sub>IH</sub>     | High logic level input voltage                         |                                                     | 1.4                    |      |              | V     |

| V <sub>IL</sub>     | Low logic level input voltage                          |                                                     |                        |      | 0.8          | V     |

**Electrical characteristics** ST7540

**Table 5. Electrical characteristics** (continued) (  $V_{DD}$  = +5V,  $V_{CC}$  =+9 V,  $V_{SS}$  = SV<sub>SS</sub> = GND = 0V,-40°C  $\leq$ T<sub>A</sub>  $\leq$ 85°C, T<sub>J</sub> < 125°C, unless otherwise specified)

| Symbol                 | Parameter                                                                | Test condition                                                  | Min.                      | Тур. | Max.         | Unit             |

|------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------|------|--------------|------------------|

| $V_{OH}$               | High logic level output voltage                                          | I <sub>OH</sub> = -2mA                                          | V <sub>DD</sub> -<br>0.75 |      |              | V                |

| V <sub>OL</sub>        | Low logic level output voltage                                           | I <sub>OL</sub> = 2mA                                           |                           |      | GND<br>+ 0.4 | V                |

| Oscillator             |                                                                          |                                                                 |                           |      |              |                  |

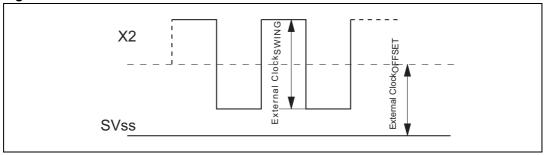

| External Clock         | X2 voltage swing                                                         | External clock. Figure 4                                        |                           | 5    |              | V <sub>pp</sub>  |

| External Clock         | X2 DC voltage level                                                      | External clock. Figure 4                                        |                           | 2.5  |              | V                |

| DC                     | XTAL Clock duty cycle                                                    | External clock.                                                 | 40                        |      | 60           | %                |

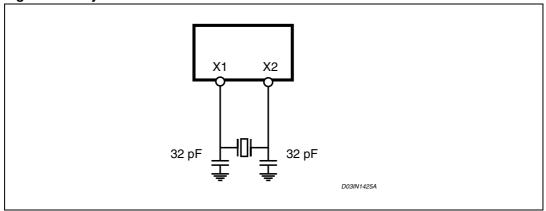

| Xtal                   | Crystal oscillator frequency                                             | fundamental                                                     |                           | 16   |              | MHz              |

| Xtal <sub>ESR</sub>    | External oscillator esr resistance                                       |                                                                 |                           |      | 40           | Ω                |

| Xtal <sub>CL</sub>     | External oscillator stabilization capacitance                            | Figure 6                                                        |                           |      | 16           | pF               |

| Transmitter            |                                                                          |                                                                 |                           |      | •            |                  |

| I <sub>TX_OUT</sub>    | Output transmitting current on TX_OUT                                    |                                                                 |                           |      | 1            | mArms            |

| V <sub>TX_OUT</sub>    | Max carrier output AC voltage                                            | $R_{CL} = 1.4k\Omega$<br>Vsense = 0V                            | 1.75                      | 2.3  | 3.5          | V <sub>PP</sub>  |

| V <sub>TX_OUTDC</sub>  | Output DC voltage on TX_OUT                                              |                                                                 | 1.7                       | 2.1  | 2.5          | V                |

| HD2 <sub>TX_OUT</sub>  | Second harmonic distortion on TX_OUT                                     | V <sub>TX_OUT</sub> = 2V <sub>PP</sub> ;<br>Fc = 86KHz, no load |                           |      | -42          | dB <sub>c</sub>  |

| HD3 <sub>TX_OUT</sub>  | Third harmonic distortion on TX_OUT                                      | V <sub>TX_OUT</sub> = 2V <sub>PP</sub> ;<br>Fc = 86KHz, no load |                           |      | -49          | dB <sub>c</sub>  |

| G accuracy             | Accuracy on voltage control loop active                                  | $R_{CL} = 0\Omega$                                              | -1                        |      | +1           | GST              |

| G <sub>ST</sub>        | ALC gain step control loop gain step                                     |                                                                 | 0.6                       | 1    | 1.4          | dB               |

| DRNG                   | ALC dynamic range                                                        |                                                                 |                           | 30   |              | dB               |

| C <sub>CL</sub>        | Input capacitance on CL pin                                              |                                                                 |                           | 80   |              | pF               |

| V <sub>senseTH</sub>   | Voltage control loop<br>reference threshold on<br>V <sub>sense</sub> pin | Figure 17                                                       | 160                       | 180  | 200          | mV <sub>PK</sub> |

| V <sub>senseHYST</sub> | Hysteresis on voltage loop reference threshold                           | Figure 17                                                       |                           | ±18  |              | mV               |

**Table 5. Electrical characteristics** (continued) (  $V_{DD}$  = +5V,  $V_{CC}$  =+9 V,  $V_{SS}$  = SV $_{SS}$  = GND = 0V,-40°C  $\leq$ T $_{A}$   $\leq$ 85°C, T $_{J}$  < 125°C, unless otherwise specified)

| Symbol                   | Parameter                                                                               | Test condition                       | Min. | Тур. | Max. | Unit      |

|--------------------------|-----------------------------------------------------------------------------------------|--------------------------------------|------|------|------|-----------|

| V <sub>SENSE</sub>       | V <sub>SENSE</sub> Input impedance                                                      |                                      |      | 36   |      | kΩ        |

| CL <sub>TH</sub>         | Current control loop<br>reference threshold on<br>CL pin                                | Figure 17                            | 1.80 | 1.90 | 2.00 | V         |

| CL <sub>HYST</sub>       | Hysteresis on current loop reference threshold                                          | Figure 17                            | 210  | 250  | 290  | mV        |

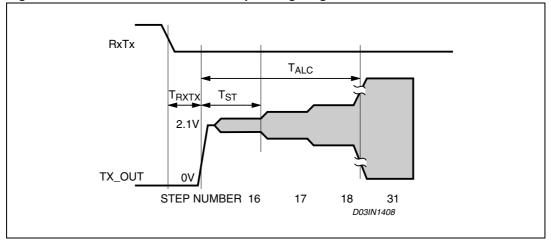

|                          |                                                                                         | Figure 21 - 600<br>Baud Xtal = 16MHz |      |      | 1.6  | ms        |

| T                        | Carrier activation time                                                                 | Figure 21- 1200 Baud<br>Xtal = 16MHz |      |      | 800  | μs        |

| T <sub>RxTx</sub>        | Carrier activation time                                                                 | Figure 21- 2400 Baud<br>Xtal = 16MHz |      |      | 400  | μs        |

|                          |                                                                                         | Figure 21- 4800 Baud<br>Xtal = 16MHz |      |      | 200  | μs        |

| T <sub>ALC</sub>         | Carrier stabilization<br>time<br>from STEP 16 to zero<br>or from step 16 to step<br>31, | Figure 21<br>Xtal = 16MHz            |      |      | 3.2  | ms        |

| T <sub>ST</sub>          | Tstep                                                                                   | Figure 21<br>Xtal = 16MHz            |      |      | 200  | μs        |

| Power amplifie           | er                                                                                      |                                      |      |      |      |           |

| PA <sub>IN(Offset)</sub> | Input terminals<br>OFFSET                                                               |                                      |      | ±18  |      | mV        |

| GBWP                     | Gain bandwidth product                                                                  |                                      | 100  |      |      | MHz       |

| R <sub>IN</sub>          | Input resistance at PA_IN+ and PA_IN-                                                   | PA_IN+ vs. Vss (1)                   | 1    |      |      | МΩ        |

| I IIN                    | pins                                                                                    | PA_IN- vs. Vss (1)                   | 1    |      |      | $M\Omega$ |

| C <sub>IN</sub>          | Input capacitance at PA_IN+ and PA_IN-                                                  | PA_IN+ vs. Vss (1)                   |      | 5    |      | pF        |

| OIN                      | pins                                                                                    | PA_IN- vs. Vss (1)                   |      | 5    |      | pF        |

| CMRR                     | Common mode rejection ratio                                                             |                                      |      | 40   |      | dB        |

**Electrical characteristics** ST7540

**Table 5. Electrical characteristics** (continued) (  $V_{DD}$  = +5V,  $V_{CC}$  =+9 V,  $V_{SS}$  = SV<sub>SS</sub> = GND = 0V,-40°C  $\leq$ T<sub>A</sub>  $\leq$ 85°C, T<sub>J</sub> < 125°C, unless otherwise specified)

| Symbol                | Parameter                                                   | Test condition                                                                                     | Min. | Тур.            | Max. | Unit              |

|-----------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|-----------------|------|-------------------|

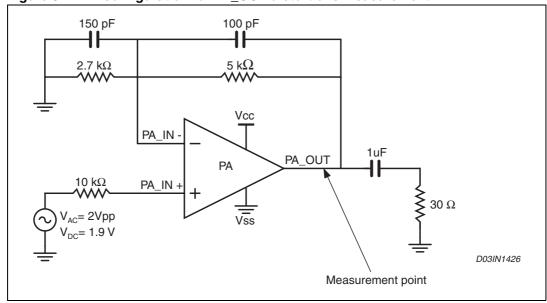

| HD2 <sub>PA_OUT</sub> | Second harmonic distortion on PA_OUT                        | $V_{PA\_OUT} = 5.6V_{PP}$ , $V_{CC} = 12V$ $R_{LOAD} = 30\Omega$ Carrier frequency: 86KHz Figure 3 |      |                 | -63  | dB <sub>c</sub>   |

| HD3 <sub>PA_OUT</sub> | Third harmonic distortion on PA_OUT pin                     | $V_{PA\_OUT} = 5.6V_{PP}$ , $V_{CC} = 12V$ $R_{LOAD} = 30\Omega$ Carrier frequency: 86KHz Figure 3 |      |                 | - 63 | dB <sub>c</sub>   |

| Receiver              |                                                             |                                                                                                    |      |                 |      |                   |

|                       | Input sensitivity<br>(Normal Mode)                          |                                                                                                    |      | 0.5             | 2    | mV <sub>rms</sub> |

| V <sub>IN</sub>       | Input sensitivity (High Sens.)                              |                                                                                                    |      | 250             |      | $\mu V_{rms}$     |

|                       | Input sensitivity (TxD line forced to "1")                  |                                                                                                    |      | V <sub>BU</sub> |      | dΒ/<br>μVrms      |

| V <sub>IN</sub>       | Maximum input signal                                        |                                                                                                    |      |                 | 2    | $V_{rms}$         |

| R <sub>IN</sub>       | Input impedance                                             |                                                                                                    | 80   | 100             | 140  | kΩ                |

|                       | Carrier detection<br>sensitivity<br>(Normal Mode)           |                                                                                                    |      | 0.5             | 2    | $mV_{rms}$        |

| $V_{CD}$              | Carrier detection<br>sensitivity<br>(High Sensitivity Mode) |                                                                                                    |      | 250             |      | $\mu V_{rms}$     |

|                       | Carrier detection sensitivity (TxD forced to "1")           |                                                                                                    |      | V <sub>BU</sub> |      | dΒ/<br>μVrms      |

| V <sub>BU</sub>       | Band in Use Detection<br>Level                              |                                                                                                    |      | 83.5            | 86   | dΒ/<br>μVrms      |

**Table 5. Electrical characteristics** (continued) (  $V_{DD}$  = +5V,  $V_{CC}$  =+9 V,  $V_{SS}$  = SV $_{SS}$  = GND = 0V,-40°C  $\leq$ T $_{A}$   $\leq$ 85°C, T $_{J}$  < 125°C, unless otherwise specified)

| Symbol            | Parameter                                     | Test condition                                               | Min. | Тур.                        | Max. | Unit                 |  |  |  |  |

|-------------------|-----------------------------------------------|--------------------------------------------------------------|------|-----------------------------|------|----------------------|--|--|--|--|

| 5V Voltage re     | 5V Voltage regulator                          |                                                              |      |                             |      |                      |  |  |  |  |

| VDC               | Linear regulator output voltage               | 0 < lo < 50mA<br>7.5V < V <sub>CC</sub> < 13.5V              | F0/  |                             | +5%  | V                    |  |  |  |  |

| 3.3V Voltage i    | regulator                                     |                                                              |      |                             |      |                      |  |  |  |  |

| $V_{DD}$          | Linear regulator output voltage               | 0 < lo < 50mA<br>7.5V < V <sub>CC</sub> < 13.5V              | -5%  | 3.3                         | +5%  | ٧                    |  |  |  |  |

| Other functio     | ns                                            |                                                              | •    | •                           |      |                      |  |  |  |  |

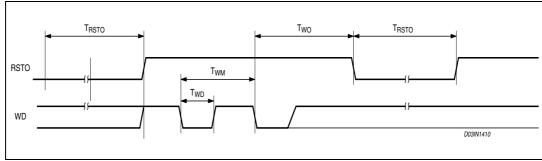

| T <sub>RSTO</sub> | Reset time                                    | See <i>Figure 23</i> ;<br>Xtal = 16MHz                       | 50   |                             |      | ms                   |  |  |  |  |

| T <sub>WD</sub>   | Watch-dog pulse width                         | See Figure 23                                                | 125  |                             |      | ns                   |  |  |  |  |

| T                 | Watch-dog pulse                               | Minimum value.<br>See <i>Figure 23</i>                       | 250  |                             |      | ns                   |  |  |  |  |

| $T_{WM}$          | period                                        | Maximum value.<br>See <i>Figure 23</i>                       |      |                             | 1490 | ms                   |  |  |  |  |

| $T_WO$            | Watch-dog time out                            | See Figure 23                                                |      |                             | 1.5  | s                    |  |  |  |  |

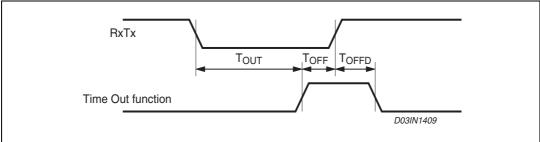

| T <sub>OUT</sub>  | TX time out                                   | Control register bit 7 and bit 8                             |      | 1 3                         |      | s                    |  |  |  |  |

| T <sub>OFF</sub>  | Time Out OFF time                             | Figure 22                                                    | 125  |                             |      | ms                   |  |  |  |  |

| T <sub>OFFD</sub> | RxTx 0->1 vs. time out delay                  | Figure 22                                                    |      |                             | 20   | μs                   |  |  |  |  |

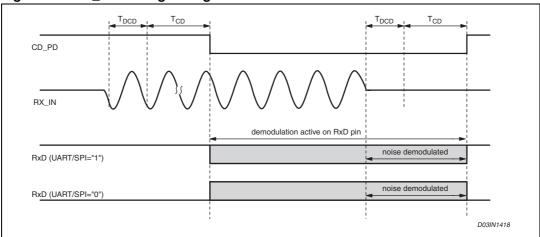

| T <sub>CD</sub>   | Carrier detection time selectable by register | Control register<br>bit 9 and bit10<br>Figure 14             |      | 500<br>1<br>3<br>5          |      | μs<br>ms<br>ms<br>ms |  |  |  |  |

| T <sub>DCD</sub>  | CD_PD Propagation delay                       | Figure 14                                                    |      | 300                         | 500  | μs                   |  |  |  |  |

| M <sub>CLK</sub>  | Master clock output selectable by register    | Control register<br>bit 15 and bit 16<br>See <i>Table 12</i> |      | fclock/2<br>fclock/4<br>off |      | MHz                  |  |  |  |  |

| BAUD              | Baud rate                                     | Control register<br>bit 3 and bit 4<br>See <i>Table 12</i>   |      | 600<br>1200<br>2400<br>4800 |      | Baud                 |  |  |  |  |

**577**

Electrical characteristics ST7540

Table 5. Electrical characteristics (continued)

(  $V_{DD}$  = +5V,  $V_{CC}$  =+9 V,  $V_{SS}$  = SV  $_{SS}$  = GND = 0V,-40°C  $\leq$  T  $_{A}$   $\leq$  85°C, T  $_{J}$  < 125°C, unless otherwise specified)

| Symbol           | Parameter                      | Test condition                                           | Тур.              | Max.                      | Unit              |    |  |  |  |  |  |

|------------------|--------------------------------|----------------------------------------------------------|-------------------|---------------------------|-------------------|----|--|--|--|--|--|

| Serial Interface |                                |                                                          |                   |                           |                   |    |  |  |  |  |  |

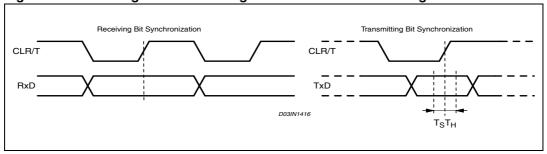

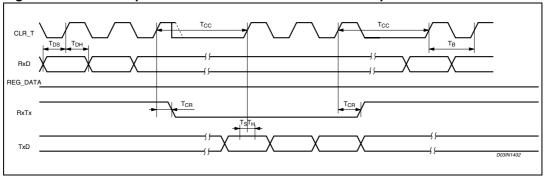

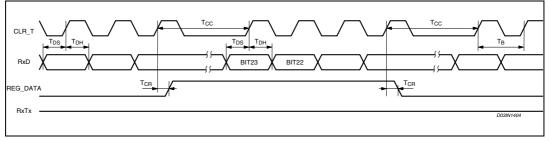

| T <sub>B</sub>   | Baud rate Bit Time<br>(1/BAUD) | Control register bit 3 and bit 4 (See <i>Figure 13</i> ) |                   | 1667<br>833<br>417<br>208 |                   | μs |  |  |  |  |  |

| Ts               | Setup time                     | see Figures 8, 9, 10, 11<br>& 12                         |                   |                           | 5                 | ns |  |  |  |  |  |

| T <sub>H</sub>   | Hold time                      | see Figures 8, 9, 10, 11<br>& 12                         |                   |                           | 2                 | ns |  |  |  |  |  |

| T <sub>CR</sub>  | CLR/T vs. REG_DATA or RxTx     | see Figures 8, 9, 10, 11<br>& 12                         |                   |                           | T <sub>B</sub> /4 |    |  |  |  |  |  |

| T <sub>CC</sub>  | CLR/T vs. CLR/T                | see Figures 8, 9, 10, 11<br>& 12                         | T <sub>B</sub>    |                           | 2*T <sub>B</sub>  |    |  |  |  |  |  |

| T <sub>DS</sub>  | Setup time                     | see Figures 8, 9, 10, 11<br>& 12                         | T <sub>B</sub> /4 |                           | T <sub>B</sub> /2 |    |  |  |  |  |  |

| T <sub>DH</sub>  | Hold time                      | see Figures 8, 9, 10, 11<br>& 12                         | T <sub>B</sub> /4 |                           | T <sub>B</sub> /2 |    |  |  |  |  |  |

| T <sub>CRP</sub> |                                |                                                          | T <sub>H</sub>    |                           | T <sub>B</sub> /2 |    |  |  |  |  |  |

<sup>1.</sup> Not tested, guaranteed by design

Figure 3. PLI configuration for PA\_OUT distortions measurement

# 5 Crystal resonator and external clock

Figure 4. External clock waveform

Figure 5. Crystal Resonator

# 6 Functional description

## 6.1 Carrier frequencies

ST7540 is a multi frequency device: eight programmable Carrier Frequencies are available (see *Table 6*).

Only one Carrier can be used a time. The communication channel could be varied during the normal working Mode to realize a multi frequency communication.

Selecting the desired frequency in the Control Register the Transmission and Reception filters are accordingly tuned.

**Table 6. Channels List**

| FCarrier          | F (KHz) |

|-------------------|---------|

| F0                | 60      |

| F1                | 66      |

| F2                | 72      |

| F3                | 76      |

| F4                | 82.05   |

| F5                | 86      |

| F6                | 110     |

| F7 <sup>(1)</sup> | 132.5   |

<sup>1.</sup> Default value

#### 6.2 Baud rates

ST7540 is a multi Baud rate device: four Baud Rate are available (See *Table 8*).

Table 7. ST7540 mark and space tones frequency distance Vs. baud rate and deviation

| Baud Rate [Baud]    | ∆F <sup>(1)</sup> (Hz)      | Deviation <sup>(2)</sup> |

|---------------------|-----------------------------|--------------------------|

| 600                 | 600                         | 1 (3)                    |

| 1200                | 600<br>1200                 | 0.5<br>1                 |

| 2400 <sup>(4)</sup> | 1200 <sup>(4)</sup><br>2400 | 0.5<br>1                 |

| 4800                | 2400<br>4800                | 0.5<br>1                 |

<sup>1.</sup> Frequency deviation

<sup>2.</sup> Deviation =  $\Delta F$  / (Baud Rate)

<sup>3.</sup> Deviation 0.5 not allowed

<sup>4.</sup> Default value

## 6.3 Mark and space frequencies

Mark and Space Communication Frequencies are defined by the following formula:

$F(0) = FCarrier + [\Delta F]/2$

F ("1") = FCarrier -  $[\Delta F]/2$

$\Delta F$  is the Frequency Deviation.

With Deviation = "0.5" the difference in terms of frequency between the mark and space tones is half the Baudrate value ( $\Delta F$ =0.5\*BAudrate). When the Deviation = "1" the difference is the Baudrate itself ( $\Delta F$ = Baudrate). The minimal Frequency Deviation is 600Hz.

Table 8. ST7540 synthesized frequencies

| Carrier frequency | Baud<br>rate | Deviation | [H    | equency<br>lz]<br>:16MHz) | Carrier frequency | Baud<br>rate | Deviation | [H     | equency<br> z]<br>:16MHz) |

|-------------------|--------------|-----------|-------|---------------------------|-------------------|--------------|-----------|--------|---------------------------|

| (KHz)             |              |           | "1"   | "0"                       | (KHz)             |              |           | "1"    | "0"                       |

|                   | 600          |           |       |                           |                   | 600          |           |        |                           |

|                   | 000          | 1         | 59733 | 60221                     |                   | 000          | 1         | 81706  | 82357                     |

|                   | 1200         | 0.5       | 59733 | 60221                     |                   | 1200         | 0.5       | 81706  | 82357                     |

| 60                | 1200         | 1         | 59408 | 60547                     | 82.05             | 1200         | 1         | 81380  | 82682                     |

| 00                | 2400         | 0.5       | 59408 | 60547                     | 62.03             | 2400         | 0.5       | 81380  | 82682                     |

|                   | 2400         | 1         | 58757 | 61198                     |                   | 2400         | 1         | 80892  | 83171                     |

|                   | 4800         | 0.5       | 58757 | 61198                     |                   | 4800         | 0.5       | 80892  | 83171                     |

|                   | 4000         | 1         | 57617 | 62337                     |                   | 4000         | 1         | 79590  | 84473                     |

|                   | 600          |           |       |                           | 86                | 600          | -         |        |                           |

|                   |              | 1         | 65755 | 66243                     |                   |              | 1         | 85775  | 86263                     |

|                   | 1200         | 0.5       | 65755 | 66243                     |                   | 1200         | 0.5       | 85775  | 86263                     |

| 66                |              | 1         | 65430 | 66569                     |                   | 1200         | 1         | 85449  | 86589                     |

|                   | 2400         | 0.5       | 65430 | 66569                     |                   | 2400         | 0.5       | 85449  | 86589                     |

|                   |              | 1         | 64779 | 67220                     |                   | 2400         | 1         | 84798  | 87240                     |

|                   | 4800         | 0.5       | 64779 | 67220                     |                   | 4800         | 0.5       | 84798  | 87240                     |

|                   | 4000         | 1         | 63639 | 68359                     |                   | 4000         | 1         | 83659  | 88379                     |

|                   | 600          |           |       |                           |                   | 600          |           |        |                           |

|                   | 000          | 1         | 71777 | 72266                     |                   | 000          | 1         | 109701 | 110352                    |

|                   | 1200         | 0.5       | 71777 | 72266                     |                   | 1200         | 0.5       | 109701 | 110352                    |

| 72                | 1200         | 1         | 71452 | 72591                     | 110               | 1200         | 1         | 109375 | 110677                    |

| 12                | 2400         | 0.5       | 71452 | 72591                     |                   | 2400         | 0.5       | 109375 | 110677                    |

|                   | 2400         | 1         | 70801 | 73242                     |                   | 2400         | 1         | 108724 | 111165                    |

|                   | 4800         | 0.5       | 70801 | 73242                     |                   | 4800         | 0.5       | 108724 | 111165                    |

|                   | 4800         | 1         | 69661 | 74382                     |                   | 4800         | 1         | 107585 | 112467                    |

|      | ,    |     |       |       |       |      |     |        |        |

|------|------|-----|-------|-------|-------|------|-----|--------|--------|

|      | 600  |     |       |       |       | 600  |     |        |        |

|      | 000  | 1   | 75684 | 76335 |       | 000  | 1   | 132161 | 132813 |

|      | 1200 | 0.5 | 75684 | 76335 |       | 1200 | 0.5 | 132161 | 132813 |

| 76   | 1200 | 1   | 75358 | 76660 | 132.5 |      | 1   | 131836 | 133138 |

| 76   | 2400 | 0.5 | 75358 | 76660 | 132.5 |      | 0.5 | 131836 | 133138 |

| 4800 | 2400 | 1   | 74870 | 77148 |       |      | 1   | 131348 | 133626 |

|      | 4900 | 0.5 | 74870 | 77148 |       | 4000 | 0.5 | 131348 | 133626 |

|      | 4000 | 1   | 73568 | 78451 |       | 4800 | 1   | 130046 | 134928 |

Table 8. ST7540 synthesized frequencies

#### 6.4 ST7540 Mains access

ST7540 can access the Mains in two different ways:

- Synchronous access

- Asynchronous access

The choice between the two types of access can be performed by means of Control Register bit 14(see *Table 12*) and affects the ST7540 data flow in Transmission Mode as in Reception Mode (for how to set the communication Mode, see *Section 6.5*).

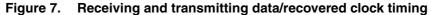

#### In data transmission mode:

- Synchronous Mains access: on clock signal provided by ST7540 (CLR/T line) rising edge, data transmission line (TxD line) value is read and sent to the FSK Modulator. ST7540 manages the Transmission timing according to the BaudRate Selected.

- Asynchronous Mains access: data transmission line (TxD line) value enters directly to the FSK Modulator. The Host Controller manages the Transmission timing (CLR/T line should be neglected).

#### In data reception mode:

- Synchronous Mains access: on clock signal recovered by a PLL from ST7540 (CLR/T line) rising edge, value on FSK Demodulator is read and put to the data reception line (RxD line). ST7540 recovers the bit timing timing according to the BaudRate Selected.

- Asynchronous Mains access: Value on FSK Demodulator is sent directly to the data reception line (RxD line). The Host Controller recovers the communication timing (CLR/T line should be neglected).

### 6.5 Host processor interface

ST7540 exchanges data with the host processor through a serial interface.

The data transfer is managed by REG\_DATA and RxTx Lines, while data are exchanged using RxD, TxD and CLR/T lines.

Four are the ST7540 working modes:

- Data Reception

- Data Transmission

- Control Register Read

- Control Register Write

REG\_DATA and RxTx lines are level sensitive inputs.

Table 9. Data and Control register access bits configuration

|                        | REG_DATA | RxTx |

|------------------------|----------|------|

| Data Transmission      | 0        | 0    |

| Data Reception         | 0        | 1    |

| Control Register Read  | 1        | 1    |

| Control Register Write | 1        | 0    |

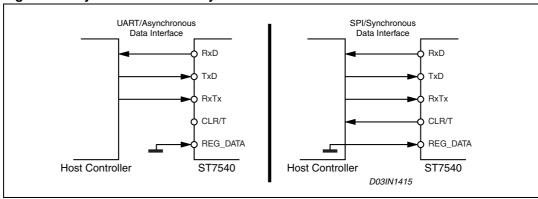

ST7540 features two type of Host Communication Interfaces:

- SPI

- UART

The selection can be done through the UART/SPI pin. If UART/SPI pin is forced to "0" SPI interface is selected while if UART/SPI pin is forced to "1" UART interface is selected. The type of interface affects the Data Reception by setting the idle state of RxD line. When ST7540 is in Receiving mode (REG\_DATA="0" and RxTx ="1") and no data are available on mains (or RxD is forced to an idle state, i.e. with a conditioned Detection Method), the RxD line is forced to "0" when UART/SPI pin is forced to "0" or it is forced to "1" when UART/SPI pin is forced to "1".

The UART interface allows to connect an UART compatible device while SPI interface allows to connect an SPI compatible device. The allowed combinations of Host Interface/ST7540 Mains Access are:

Table 10. Host interface / ST7540 mains access combinations

| Host device    | UART/SPI pin  | Communication | Mains access |             |  |  |

|----------------|---------------|---------------|--------------|-------------|--|--|

| interface type | OAN1/SPI pili | mode          | Asynchronous | Synchronous |  |  |

| UART           | "1"           | Transmission  | Х            |             |  |  |

| UART           | "1"           | Reception     | Х            |             |  |  |

| SPI            | "0"           | Transmission  |              | Х           |  |  |

| SPI            | "0"           | Reception     |              | Х           |  |  |

Figure 6. Synchronous and Asynchronous ST7540/Host Controller interfaces

ST7540 allows to interface the Host Controller using a five line interface (RxD,TxD,RxTx, CLR/T, & REG\_DATA) in case of Synchronous mains access or using a 3 line interface (RxD,TxD & RxTx) in Asynchronous mains access. Since Control Register is not accessible in Asynchronous mode, in this case REG\_DATA pin must be tied to GND.

#### 6.5.1 Communication between Host and ST7540

The Host can achieve the Mains access by selecting REG\_DATA="0" and the choice between Data Transmission or Data Reception is performed by selecting RxTx line (if RxTx ="1" ST7540 receives data from mains, if RxTx="0" ST7540 transmits data over the mains).

Communication between Host and ST7540 is different in Asynchronous and Synchronous mode:

#### Asynchronous mode:

In Asynchronous Mode, data are exchanged without any data Clock reference. The host controller has to recover the clock reference in receiving Mode and control the Bit time in transmission mode.

If RxTx line is set to "1" & REG\_DATA="0" (Data Reception), ST7540 enters in an Idle State. After Tcc time the modem starts providing received data on RxD line.

If RxTx line is set to "0" & REG\_DATA="0" (Data Transmission), ST7540 enters in an Idle State and transmission circuitry is switched on. After Tcc time the modem starts transmitting data present on TxD line.

#### Synchronous mode:

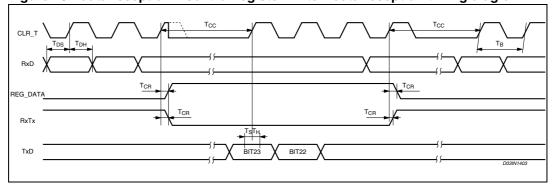

In Synchronous Mode ST7540 is always the master of the communication and provides the clock reference on CLR/T line. When ST7540 is in receiving mode an internal PLL recovers the clock reference. Data on RxD line are stable on CLR/T rising Edge.

When ST7540 is in transmitting mode the clock reference is internally generated and TxD line is sampled on CLR/T rising Edge.

If RxTx line is set to "1" & REG\_DATA="0" (Data Reception), ST7540 enters in an Idle State and CLR/T line is forced Low. After Tcc time the modem starts providing received data on RxD line.

If RxTx line is set to "0" & REG\_DATA="0" (Data Transmission), ST7540 enters in an Idle State and transmission circuitry is switched on. After Tcc time the modem starts transmitting data present on TxD line (*Figure 8*).

Figure 8. Data reception -> data transmission -> data reception

**577**

#### 6.5.2 Control register access

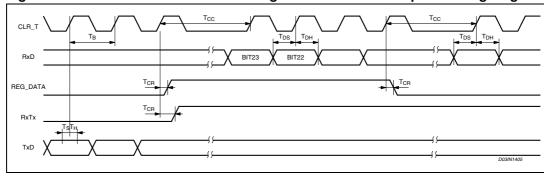

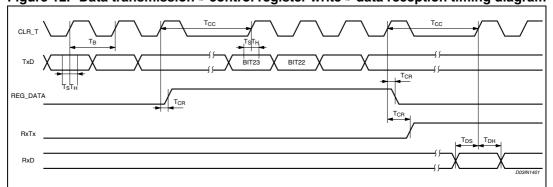

The communication with ST7540 Control Register is always synchronous. The access is achieved using the same lines of the Mains interface (RxD, TxD, RxTx and CLR/T) plus REG DATA Line.

With REG\_DATA = 1 and RxTx = 0, the data present on TxD are loaded into the Control Register MSB first. The ST7540 samples the TxD line on CLR/T rising edges. The control Register content is updated at the end of the register access section (REG\_DATA falling edge).

In Normal Control Register mode (Control Register bit 21 = "0", see *Table 12*) if more than 24 bits are transferred to ST7540 only latest 24 bits are stored inside the Control Register. If less than 24 bits are transferred to ST7540 the Control Register writing is aborted.

In order to avoid undesired Control Register writings caused by REG\_DATA line fluctuations (for example because of surge or burst on mains), in Extended Control Register mode (Control Register bit 21 = "1" see *Table 12*) exactly 24 or 48 bits must be transferred to ST7540 in order to properly write the Control Register, otherwise writing is aborted. If 24 bits are transferred, only the first 24 Control Register bits (from 23 to 0) are written.

With REG\_DATA = 1 and RxTx = 1, the content of the Control Register is sent on RxD port. The Data on RxD are stable on CLR/T rising edges MSB First. In Normal Control Register mode 24 bits are transferred from ST7540 to the Host. In Extended Control Register mode 24 or 48 bits are transferred from ST7540 to the Host depending on content of Control Register bit 18 (with bit 18 = "0" the first 24 bits are transferred, otherwise all 48 bits are transferred, see *Table 12*).

Figure 9. Data reception → control register read → data reception timing diagram

Figure 10. data reception - control register write - data reception timing diagram

Figure 11. Data transmission - control register read - data reception timing diagram

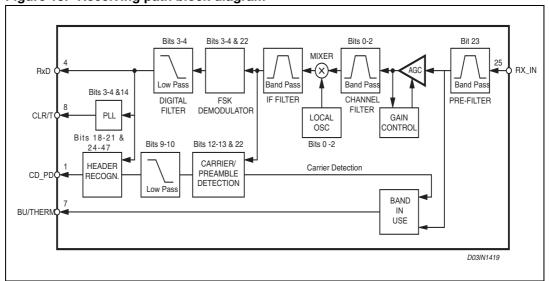

## 6.6 Receiving mode

The receive section is active when RxTx Pin ="1" and REG\_DATA=0.

The input signal is read on RX\_IN Pin using SV<sub>SS</sub> as ground reference and then pre-filtered by a Band pass Filter (62kHz max bandwidth at -3dB). The Pre-Filter can be inserted setting one bit in the Control Register. The Input Stage features a wide dynamic range to receive Signal with a Very Low Signal to Noise Ratio. The Amplitude of the applied waveform is automatically adapted by an Automatic Gain Control block (AGC) and then filtered by a Narrow Band Band-Pass Filter centered around the Selected Channel Frequency (14kHz max at -3dB). The resulting signal is down-converted by a mixer using a sinewave generated by the FSK Modulator. Finally an Intermediate Frequency Band Pass-Filter (IF Filter) improves the Signal to Noise ration before sending the signal to the FSK demodulator. The FSK demodulator then send the signal to the RX Logic for final digital filtering. Digital filtering Removes Noise spikes far from the BAUD rate frequency and Reduces the Signal Jitter. RxD Line is forced to "0" or "1" (according the UART/SPI pin level) when neither mark or space frequencies are detected on RX\_IN Pin.

Mark and Space Frequency in Receiving Mode must be distant at least BaudRate/2 to have a correct demodulation.

While ST7540 is in Receiving Mode (RxTx pin ="1"), the transmit circuitry, Power Line Interface included, is turned off. This allows the device to achieve a very low current consumption (5mA typ).

577

#### • Receiving Sensitivity Level Selection

It is possible to select the ST7540 Receiving Sensitivity Level by Control Register (see *Table 12*) or setting to '1' the TxD pin during reception phase (this condition overcomes the control register setting the sensitivity equal to BU threshold). Increasing the device sensitivity allows to improve the communication reliability when the ST7540 sensitivity is the limiting factor.

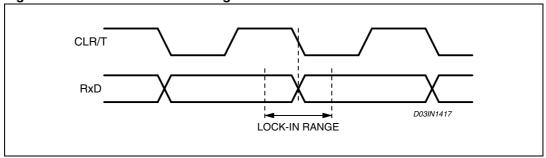

#### Synchronization Recovery System (PLL)

ST7540 embeds a Clock Recovery System to feature a Synchronous data exchange with the Host Controller. The clock recovery system is realized by means of a second order PLL. In Synchronous mode, data on the data line (RxD) are stable on CLR/T line rising edge (CLR/T Falling edge synchronized to RxD line transitions  $\pm$  LOCK-IN Range). The PLL Lock-in and Lock-out Range is  $\pm\pi/2$ . When the PLL is in the unlock condition RxD line is forced to "0" or "1" according to the UART/SPI pin level and CLR/T is forced to "0" only if the Detection Method "Preamble Detection With Conditioning" is selected. When PLL is in unlock condition it is sensitive to RxD Rising and Falling Edges. The maximum number of transition required to reach the lock-in condition is 5. When in lock-in condition the PLL is sensitive only to RxD rising Edges to reduce the CLR/T Jitter. ST7540 PLL is forced in the un-lock condition, when more than 32 equal symbols are received. Due to the fact that the PLL, in lock-in condition, is sensitive only to RxD rising edge, sequences equal or longer than 15 equal symbols can put the PLL into the un-lock condition.

#### Carrier/Preamble Detection

The Carrier/Preamble Block is a digital Frequency detector Circuit. It can be used to manage the MAINS access and to detect an incoming signal. Two are the possible setting:

- Carrier Detection

- Preamble Detection

#### Carrier Detection

The Carrier/Preamble detection Block notifies to the host controller the presence of a Carrier when it detects on the RX\_IN Input a signal with an harmonic component close to the programmed Carrier Frequency. The CD\_PD signal sensitivity is identical to the data reception sensitivity (0.5mVrms Typ. in Normal Sensitivity Mode). When the device sensitivity is set by the TxD line (Sensitivity level equal to BU threshold) the CD\_PD signal is conditioned to the BU signal.

The CD PD line is forced to a logic level low when a Carrier is detected.

#### Preamble Detection

The Carrier/Preamble detection Block notifies to the host controller the presence of a Carrier modulated at the Programmed Baud Rate for at least 4 Consecutive Symbols ("1010" or "0101" are the symbols sequences detected).

CD\_PD line is forced low till a Carrier signal is detected and PLL is in the lock-in range.

To reinforce the effectiveness of the information given by CD\_PD Block, a digital filtering is applied on Carrier or Preamble notification signal (see *Section 6.8: Control register*). The Detection Time Bits in the Control Register define the filter performance. Increasing the Detection Time reduced the false notifications caused by noise on main line. The Digital filter adds a delay to CD\_PD notification equal to the programmed Detection Time. When the carrier frequency disappears, CD\_PD line is held low for a period equal to the detection time and then forced high. During this time, some spurious data caused by noise can be demodulated and sent over RxD line.

#### Header Recognition

In Control Register Extended Mode (Control Register bit 21="1", see *Table 12*) the CD\_PD line can be used to recognize if an header has been sent during the transmission. With Header Recognition function enable (Control Register bit 18="1", see *Table 12*), CD\_PD line is forced low when a Frame Header is detected. If Frame Length Count function is enabled, CD\_PD is held low and a number of 16 bit word equal to the Frame Length selected is sent to the host controller. In this case, CLR/T is forced to "0" and RxD is forced to "0" or "1" (according the UART/SPI pin level) when Header has not been detected or after the Frame Length has been reached. If Frame Length Count function is disabled, an header recognition is signaled by forcing CD\_PD low for one period of CLR/T line. In this case, CLR/T and RxD signal are always present, even if no header has been recognized.

Figure 14. CD\_PD Timing during RX

Figure 15. Receiving path block diagram

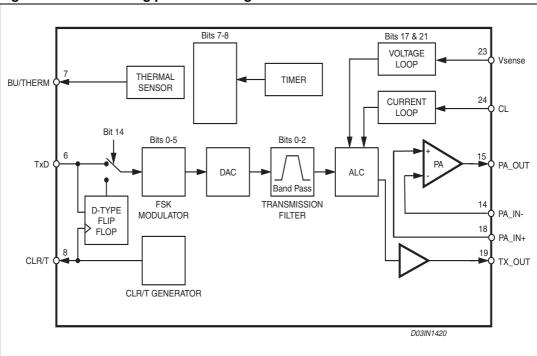

#### 6.7 Transmission mode

The transmission mode is set when RxTx Pin ="0" and REG\_DATA Pin ="0". In transmitting mode the FSK Modulator and the Power Line Interface are turned ON. The transmit Data (TxD) enter synchronously or asynchronously to the FSK modulator.

- Synchronous Mains access: on CLR/T rising edge, TxD Line Value is read and sent to the FSK Modulator. ST7540 manages the Transmission timing according to the BaudRate Selected

- Asynchronous Mains access: TxD data enter directly to the FSK Modulator. The Host Controller manages the Transmission timing

In both conditions no Protocol Bits are added by ST7540.

The FSK frequencies are synthesized in the FSK modulator from a 16 MHz crystal oscillator by direct digital synthesis technique. The frequencies Table in different Configuration is reported in *Table 8*. The frequencies precision is same as external crystal one's.

In the analog domain, the signal is filtered in order to reduce the output signal spectrum and to reduce the harmonic distortion. The transition between a symbol and the following is done at the end of the on-going half FSK sinewave cycle.

Figure 16. Transmitting path block diagram

#### Automatic Level Control (ALC)

The Automatic Level Control Block (ALC) is a variable gain amplifier (with 32 non linear discrete steps) controlled by two analog feed backs acting at the same time. The ALC gain range is 0dB to 30 dB and the gain change is clocked at 5KHz. Each step increases or reduces the voltage of 1dB (Typ).

Two are the control loops acting to define the ALC gain:

- A Voltage Control loop

- A Current Control Loop

<u>The Voltage control loop</u> acts to keep the Peak-to-Peak Voltage constant on Vsense. The gain adjustment is related to the result of a peak detection between the Voltage waveform on Vsense and two internal Voltage references. It is possible to protect the Voltage Control Loop against noise by freezing the output level (see <u>Section 7.5</u>: <u>Output voltage level freeze</u>).

- If Vsense < Vsense<sub>TH</sub> Vsense<sub>HYST</sub>

The next gain level is increased by 1 step

- If Vsense<sub>TH</sub> Vsense<sub>HYST</sub> < Vsense < Vsense<sub>TH</sub> + Vsense<sub>HYST</sub> No Gain Change

- If Vsense > Vsense<sub>TH</sub> + Vsense<sub>HYST</sub> The next gain level is decreased by 1 step

The Current control loop acts to limit the maximum Peak Output current inside PA\_OUT.

The current control loop acts through the voltage control loop decreasing the Output Peak-to-Peak Amplitude to reduce the Current inside the Power Line Interface. The current sensing is done by mirroring the current in the High side MOS of the Power Amplifier (not dissipating current Sensing). The Output Current Limit (up to 500mrms), is set by means of an external resistor ( $R_{CL}$ ) connected between CL and  $V_{SS}$ . The resistor converts the current sensed into a voltage signal. The Peak current sensing block works as the Output Voltage sensing Block:

- If V(CL) < CL<sub>TH</sub> CL<sub>HYST</sub>Voltage Control Loop Acting

- If CL<sub>TH</sub> CL<sub>HYST</sub> < V(CL) < CL<sub>TH</sub> + CL<sub>HYST</sub>No Gain Change

- If V(CL) > CL<sub>TH</sub> + CL<sub>HYST</sub>The next gain level is decreased by 1 step

Figure 17 shows the typical connection of Current an Voltage control loops.

Vout<sub>PK</sub> \_OUT/TX\_OUT Vout R1 VOLTAGE LOOP 1.865V (Typ) CURRENT LOOP VCL<sub>HYST</sub> Vclth D03IN1421

Figure 17. Voltage and current feedback external interconnection example

Voltage Control Loop Formula

$$V_{OUTPK} \cong \frac{R_1 + R_2}{R_2} \cdot (Vsense_{TH} \pm Vsense_{HYST})$$

| Table 11. VOUT V | able 11. VOUT VS. AT & AZ TESISTOTS VALUE |            |         |         |  |  |  |  |  |  |  |

|------------------|-------------------------------------------|------------|---------|---------|--|--|--|--|--|--|--|

| Vout (Vrms)      | Vout (dBμV)                               | (R1+R2)/R2 | R2 (KΩ) | R1 (KΩ) |  |  |  |  |  |  |  |

| 0.150            | 103.5                                     | 1.1        | 7.5     | 1.0     |  |  |  |  |  |  |  |

| 0.250            | 108.0                                     | 1.9        | 5.1     | 3.9     |  |  |  |  |  |  |  |

| 0.350            | 110.9                                     | 2.7        | 3.6     | 5.6     |  |  |  |  |  |  |  |

| 0.500            | 114.0                                     | 3.7        | 3.3     | 8.2     |  |  |  |  |  |  |  |

| 0.625            | 115.9                                     | 4.7        | 3.3     | 11.0    |  |  |  |  |  |  |  |

| 0.750            | 117.5                                     | 5.8        | 2.7     | 12.0    |  |  |  |  |  |  |  |

| 0.875            | 118.8                                     | 6.6        | 2.0     | 11.0    |  |  |  |  |  |  |  |

| 1.000            | 120.0                                     | 7.6        | 1.6     | 10.0    |  |  |  |  |  |  |  |

| 1.250            | 121.9                                     | 9.5        | 1.6     | 13.0    |  |  |  |  |  |  |  |

| 1.500            | 123.5                                     | 10.8       | 1.6     | 15.0    |  |  |  |  |  |  |  |

Table 11. V<sub>OUT</sub> Vs. R1 & R2 resistors value

Note:

Notes: The rate of R2 takes in account the input resistance on the  $V_{SENSE}$  pin (36K $\Omega$ ). 10nF capacitor effect has been neglected.

Figure 18. Typical output current vs RCL

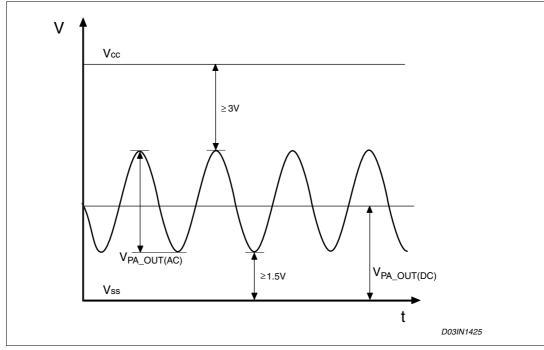

#### Integrated Power Line Interface (PLI)

The Power Amplifier (PA) is a CMOS AB Class Power Amplifier. The PA requires, to ensure a proper

operation, a regulated and well filtered Supply Voltage. Vcc Voltage and PA\_OUT Voltage must fulfil

the following formulas to work without clipping phenomena:

$$V_{CC} \ge \frac{VPAOUT(AC)}{2} + VPOUT(DC) + 3V$$

$$VPOUT(DC) - \frac{VPAOUT(AC)}{2} \ge 1.5V$$

Figure 19. PA\_OUT and  $V_{CC}$  relationship

Inputs and outputs of PA are available on pins PA\_IN-,PA\_IN+ and PA\_OUT. User can easily select an appropriate active filtering topology to filter the signal present on TX\_OUT pin. TX\_OUT output has a current capability much lower than PA\_OUT.

PA\_INPA\_OUT

PA\_INPA\_OUT

PA\_INPA\_OUT

PA\_INPA\_OUT

PA\_INPA\_INPA\_OUT

PA\_INPA\_OUT

PA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA\_INPA

Figure 20. Power line interface topology

Figure 21. Power line interface startup timing diagram

## 6.8 Control register

The ST7540 is a multi-channel and multifunction transceiver. An internal 24 or 48 Bits (in Extended mode) Control Register allows to manage all the programmable parameters (*Table 12*).

The programmable functions are:

- Channel Frequency

- Baud Rate

- Deviation

- Watchdog

- Transmission Timeout

- Frequency Detection Time

- Detection Method

- Mains Interfacing Mode

- Output Clock

- Sensitivity Mode

- Input Pre-Filter

In addition to these functions the Extended mode provides 24 additional bits and others functions:

- Output Level Freeze

- Frame Header Recognizes (one 16 bits header of or two 8 bits headers) with support to Frame Length Bit count

**Table 12. Control register functions**

|         | Function       | Value                | Se    | election | on    | Note                           | Default      |

|---------|----------------|----------------------|-------|----------|-------|--------------------------------|--------------|

|         |                |                      | Bit2  | Bit1     | Bit0  |                                |              |

|         |                | 60 KHz               | 0     | 0        | 0     |                                |              |

|         |                | 66 KHz               | 0     | 0        | 1     |                                |              |

| 0.4- 0  | <b>-</b>       | 72 KHz               | 0     | 1        | 0     |                                |              |

| 0 to 2  | Frequencies    | 76 KHz               | 0     | 1        | 1     |                                | 132.5 kHz    |

|         |                | 82.05 KHz            | 1     | 0        | 0     |                                | 102.0 1.1.12 |

|         |                | 86 KHz               | 1     | 0        | 1     |                                |              |

|         |                | 110 KHz<br>132.5 KHz | 1 1   | 1        | 0     |                                |              |

|         |                | 132.3 KHZ            |       | <u> </u> |       |                                |              |

|         |                |                      | Bit 4 | 1        | Bit 3 |                                |              |

| 0.4- 4  | David water    | 600                  | 0     |          | 0     |                                |              |

| 3 to 4  | Baud rate      | 1,200                | 0     |          | 1     |                                | 2400         |

|         |                | 2,400                | 1     |          | 0     |                                |              |

|         |                | 4,800                | 1     |          | 1     |                                |              |

|         |                |                      |       | Bit 5    |       |                                |              |

| 5       | Deviation      | 0.5                  |       | 0        |       |                                | 0.5          |

|         |                | 1                    |       | 1        |       |                                | 0.5          |

|         |                |                      |       | Bit 6    |       |                                |              |

| 6       | Watchdog       | Disabled             |       | 0        |       |                                |              |

|         |                | Enabled (1.5 s)      |       | 1        |       |                                | Enabled      |

|         |                |                      | Bit 8 | 3        | Bit 7 |                                |              |

|         | Transmission   | Disabled             | 0     |          | 0     |                                |              |

| 7 to 8  | time out       | 1 s                  | 0     |          | 1     |                                | 1 sec        |